Most disrespectful gfx gen launch I’ve seen in a good while

grow a plant, hug your dog, lift heavy, eat healthy, be a nerd, play a game and help each other out

Most disrespectful gfx gen launch I’ve seen in a good while

they fully won’t but I’d like for you to be able to play once again if you enjoyed it way back when. Hell I think they even went to far as to detect & prevent play on a Linux host when running the game through a win VM with Gfx pass through.

Ah right. Appreciate the info!

Oh right. When I first heard about Lemmy, I tried to join .ml because it was the first instance I was made aware of. I think it was being rate limited at the time due to that whole reddit exodus thing, and I wasn’t able to get through, but. .world let me sign up so here I am.

I’d like to think that members of a given instance have their own opinions. It’s sad to hear about how territorial lemmy is.

I’m not familiar with the first subreddit, what was that about?

Appreciate the explanation. I’ve seen some remarks about the instance in passing, I’ve just never paid close enough attention to how communities have interacted with each other in the past.

What’s the story with this place?

That’s on me. I come here for tech and cute stuff and it’s easy for me to miss announcements pinned at the top 😓

Sorry I’m not sure if it was reverted; I was completely unaware of it even being proposed.

fucking hell the amount of effort that would take on popular communities is insane. Was totally unaware of this policy change.

Iirc, Acton donated to signal, they didn’t go on to make it as an alternative. Signal existed long before he left, and even longer ago as open whisper systems’ TextSexure, which was a means of SMS / MMS encryption.

OWS was founded by moxie back in 2013

what a majestic game.

noble even.

check your vector.

Tanveer Singh is the one who put out this belter a while back

https://www.xda-developers.com/intel-is-better-than-amd-for-average-gamer/

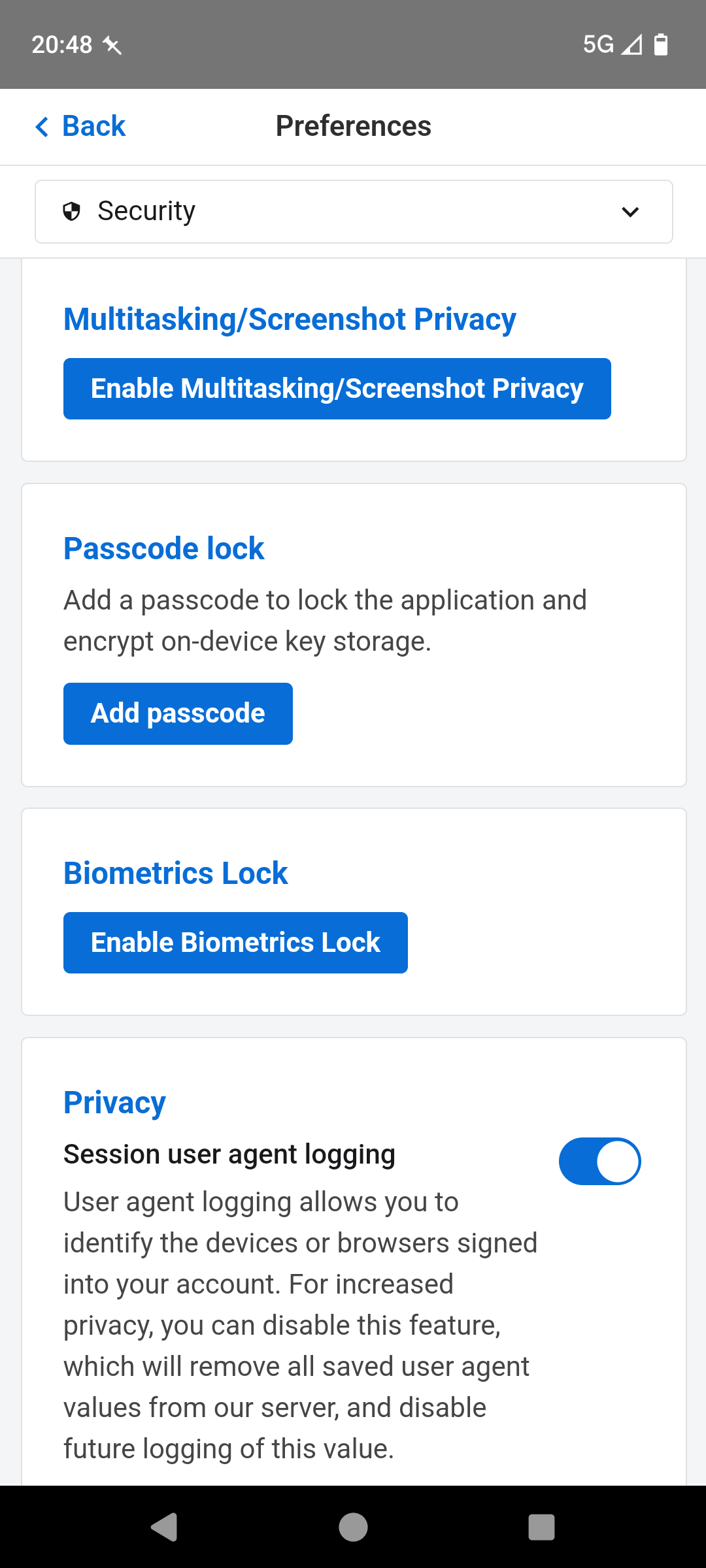

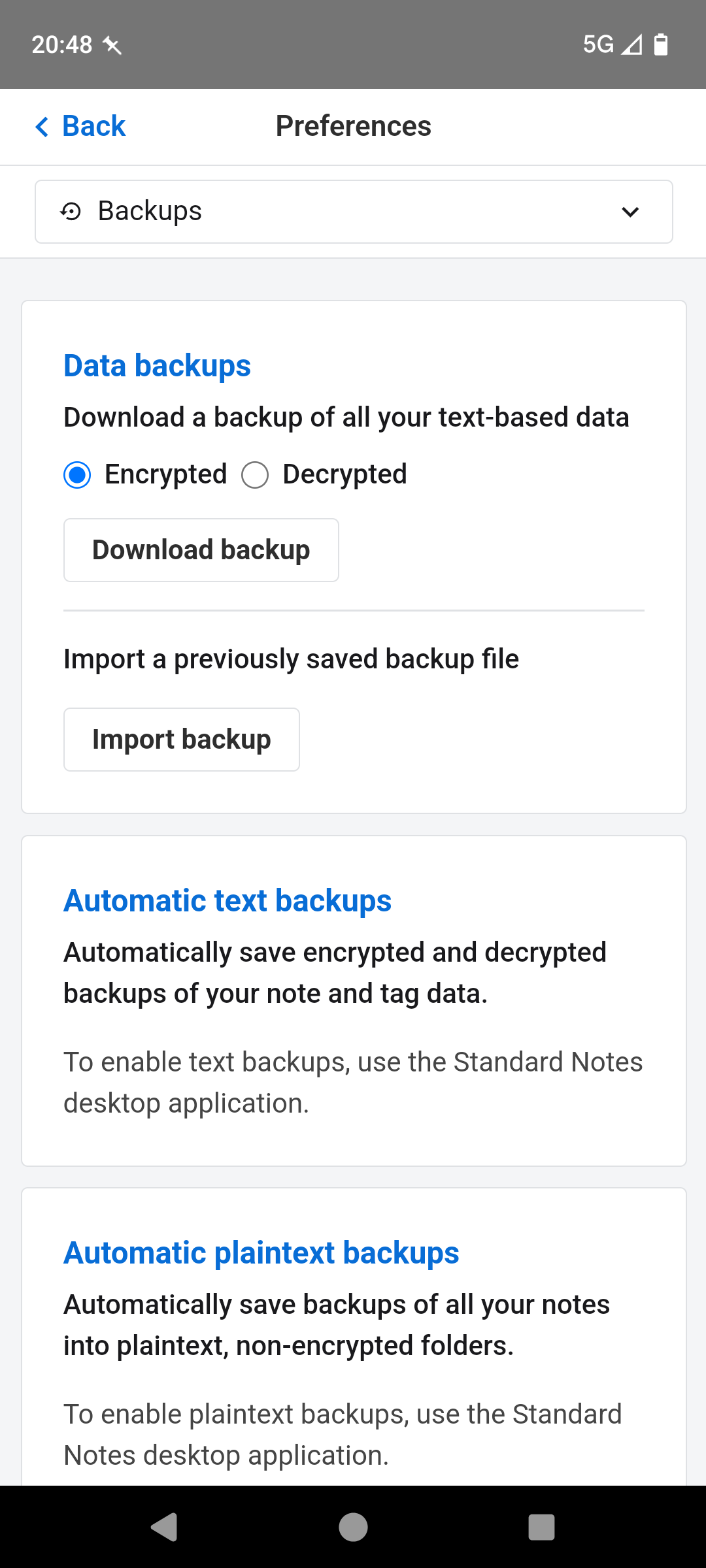

That’s fair. I quickly tested standard notes with it firewalled on my phone. it can be used offline and can be set up to require a passcode or biometric verification. Most significantly, the sync server can be self hosted, in case you do decide to pursue this avenue in the future.

The client apps are available on all platforms, including linux distros, though the desktop apps use electron and feel somewhat sluggish (it uses React Native for android and iOS which feels almost equally bad).

I’ve not attempted to use this completely offline but it seems to work acceptably. Bear in mind that the client apps can have subtle nags to subscribe to extended mode, which aren’t present when self hosting.

That said, the default user flow emphasises on the use of an account with an email address, and I’m not sure that’s what you want. I’m wondering if KeePassDX could be used for secure note taking, not sure if keepass entries have some kind of character limit though.

I’m curious about the cross platform requirement given the offline one. I’m wondering if Standard Notes or something similar can be used in a purely offline mode.

I’d hope that practically anything on Android today would suffice given the typical enforcement of either FBE/FDE. Do you specifically need an app that is password protected in addition to Android’s device security, or is this more of an ask for desktop counterparts?

Signed. Thanks for sharing

Now I’m extra mad because their new app is messing with sleepy time for the bebis 😠

fuck those guys. Glad you gave a workaround in place.

no u

Hope it works out for you tho. Hit us up if you need a hand.

I’m using my kitchen S5 exclusively in aux mode with a spare phone which runs the Malopieds fork of Innertune. It’s the perfect music kiosk / jukebox and I never have to touch their apps (unless I change up my network).

To be fair, you can at least turn this off in most (if not all) of the impacted games.